Materials Science Forum Vols. 556-557 (2007) pp 831-834

online at http://www.scientific.net/

© (2007) Trans Tech Publications, Switzerland

Online available since 2007/Sep/15

Philip G. Neudeck, David J. Spry, Liang-Yu Chen, Robert S. Okojie, Glenn M. Beheim, Roger Meredith and Terry Ferrier

NASA Glenn Research Center, 21000 Brookpark Road, M.S. 77-1, Cleveland, OH 44135 USA OAI, NASA Glenn, 21000 Brookpark Road, M.S. 77-1, Cleveland, OH 44135 USA

Keywords: High temperature, MESFET, Amplifier, Packaging, Durability, Reliability

Abstract.

While there have been numerous reports of short-term transistor operation at 500 °C or above, these devices have previously not demonstrated sufficient long-term operational durability at 500 °C to be considered viable for most envisioned applications. This paper reports the development of SiC field effect transistors capable of long-term electrical operation at 500 °C. A 6H-SiC MESFET was packaged and subjected to continuous electrical operation while residing in a 500 °C oven in oxidizing air atmosphere for over 2400 hours. The transistor gain, saturation current (IDSS), and on-resistance (RDS) changed by less than 20% from initial values throughout the duration of the biased 500 °C test. Another high-temperature packaged 6H-SiC MESFET was employed to form a simple one-stage high-temperature low-frequency voltage amplifier. This single-stage common-source amplifier demonstrated stable continuous electrical operation (negligible changes to gain and operating biases) for over 600 hours while residing in a 500 °C air ambient oven. In both cases, increased leakage from annealing of the Schottky gate-to-channel diode was the dominant transistor degradation mechanism that limited the duration of 500 °C electrical operation.

Introduction

As the reliable operating temperature envelope of integrated silicon electronics has been expanded from 125 °C to temperatures above 200 °C, these electronics have found beneficial use in aerospace, automotive, industrial, and energy production systems [1]. Further extension of the reliable operational envelope of semiconductor electronics above 300 °C is also expected to offer additional benefits to these industries, particularly in aerospace combustion engine applications where temperatures can approach 600 °C. The emergence of wide bandgap semiconductors, including silicon carbide (SiC), diamond, and gallium nitride (GaN), has enabled short-term (i.e., less than a few hours) electrical device demonstrations at ambient temperatures from 500 °C to 650 °C. However, these devices have previously not demonstrated sufficient long-term electronic durability to be considered viable for most envisioned applications at these high temperatures.

In order to begin meeting the needs of most high-temperature applications, a wide bandgap transistor technology must first demonstrate that it can achieve stable, long-term electrical operation at high temperature without significant changes in electrical operating parameters. This paper reports on the fabrication and testing of a 6H-SiC metal-semiconductor field-effect transistor (MESFET) and single-stage amplifier that respectively achieved over 2400 and 600 hours of continuous electrical operation in 500 °C air ambient with less than 20% change in electrical parameters.

Experimental

Small-signal 6H-SiC epitaxial-channel MESFET’s with nitrogen-implanted source-drain contact regions were fabricated starting from commercially purchased substrates with customized epilayers. Fig. 1 shows a simplified schematic cross-section of the MESFET device structure. For 500 °C durability, the fabrication process features multiple levels of high temperature metallization (Ti/TaSi/Pt stack [2]) for durable electrical contacts (ohmic and Schottky) and dielectric passivation (SiO2 and Si3N4) aimed at preventing contamination (particularly oxygen) from reaching electrically sensitive interfaces. MESFET fabrication process details as well as initial durability testing (up to 500 hours at 500 °C) were previously described in [3]. Due to a processing error (described in [3]), the gate fingers only spanned about 95% of the MESFET channel, which resulted in a small parasitic shunt source-to-drain current path (through the ~ 5% of the channel uncovered by the gate finger) that prevented complete transistor pinch-off.

Fig. 1. Simplified schematic cross-section of 6H-SiC MESFET [3].

A few MESFET chips were packaged for prolonged high temperature testing using a ceramic substrate and Au-thick-film metallization based high temperature packaging approach described in [4]. The chip packages were in turn mounted on a simple ceramic-based circuit board with 10 mil diameter Au wire leads attached to Au-thick-film patterned interconnect traces. Prolonged 500 °C electrical testing was carried out with boards (including SiC devices) residing in a temperaturecontrolled bench-top oven in air ambient, with the Au wire leads running outside the oven to the electrical test instruments (via terminal strip connection to conventional instrument cables). The transistor source terminals were grounded for all electrical measurements. One circuit board was assembled into a simple common-source amplifier stage with a SiC MESFET and epitaxial SiC resistors. Far more comprehensive descriptions of the amplifier circuit, components, packaging, and initial electrical testing (during unbiased 500 °C heat soak up to 432 hours) are available in [4].

Results

Fig. 2 displays the measured 500 °C drain current vs. voltage characteristics of the discrete 6H-SiC MESFET Device #1 at the start of the test (thin darker lines) and following 2457 hours (thick lighter lines) of continuous 500 °C 60 Hz curve tracer bias testing. Fig. 3 shows the change in relevant 500 °C transistor electrical parameters throughout the 500 °C bias testing. With the exception of gate leakage, all transistor parameters plotted in Fig. 3 exhibit less than 20% change over the course of the 2457 hours of 500 °C electrical testing. The device did not exhibit significant looping or threshold voltage (VT) hysteresis despite prolonged application and removal of negative substrate bias during testing and a thermal cycle to room temperature [3].

Fig. 2. Packaged 6H-SiC MESFET I-V characteristics measured at beginning and end of prolonged curve-tracer biasing at 500 °C in air. Gate steps are -2V starting from top trace of VG = 0 V, and VSubstrate = -20 V.

Both Fig. 2 and Fig. 3 evidence that increased leakage current from the reverse-biased Schottky gate-to-channel diode is the dominant device degradation mechanism. For example, all drain current seen in Fig. 2 at drain bias VD = 0 V (also plotted as “Gate Leakage” in Fig. 3) must arise from gateto-channel diode leakage as increasing negative (reverse) bias is applied to the gate terminal (VG = 0V to -20 V in -2V steps), due to the fact that drain-to-source current flow through the channel is zero with VD = 0 V. The maximum leakage current (which occurs for the largest gate bias step of VG = -20 V) is clearly much higher for the measured 2457-hour characteristics at all drain voltages.

Fig. 3. Measured electrical parameters of 6HSiC MESFET vs. biased operating time at 500 °C. IDSS and Gain are measured at VDS = 20 V, while RDS and Gate Leakage are measured at VDS = 0 V. VSubtrate = -20 V.

The addition of this increased gate leakage current clearly worsens transistor turn-off and output conductance (Fig. 2) that are already non-optimal due to the parasitic shunt current path mentioned in the previous section. As the increasing gate leakage current becomes a larger percentage of the overall drain current, transistor gain (i.e., ID/ VG) also degrades. It is important to note that channel resistance (RDS) does not degrade, indicating that no significant degradation of the ohmic contacts and packaging connections occurred.

Fig. 4. Schematic of amplifier stage tested at 500 °C [4]. VDD = 120 V, VGate Bias = -9 V, VSubstrate = -20 V, Cext = 0.47 IF, RG = 150 k , and RD = 340

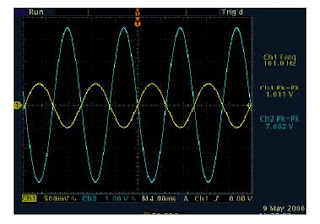

Fig. 5. Sine wave input (1 V peak-to-peak) and output (7 V peak-to-peak) waveforms recorded during the 430th hour of amplifier stage electric al operation at 500 °C.

Figs. 4, 5, and 6 briefly summarize the results of the simple voltage amplifier stage board constructed using a second 6H-SiC MESFET (Device #2). The amplifier board was subjected to 656 hours of unbiased 500 °C heat soaking prior to initiation of 500 °C continuous electrical operation. Fig. 4 shows the circuit schematic with the dotted box showing the parts of the circuit on the board tested in the 500 °C oven. For this initial low-frequency demonstration, the amplifier output wire was connected via RG-58 BNC cable directly into a 1 M-ohm AC-coupled digitizing oscilloscope input, and an external (room temperature) coupling capacitor was also required at the amplifier input as the 500 °C on-board capacitor was too small to support low-frequency (~100 Hz) operation [4]. Fig. 5 shows the sine wave input and output voltage waveforms measured in the 430th hour of continuous 500 °C electrical operation (in addition to 656 hours of unbiased 500 °C heat soak). Circuit power supply biases were held constant throughout the 500 °C electrical test duration. Fig. 6 shows measured voltage gain vs. frequency performance after various periods of continuous electrical operation at 500 °C. The amplifier gain remained stable (within 20% of original value) for over 600 hours of continuous 500 °C electrical operation (over 1300 hours total soak time at 500 °C). Between 668 and 1300 hours of electrically biased test time, a severe degradation in amplifier gain is observed. Curve-tracer characterization of MESFET Device #2 recorded at the beginning and end the 500 °C testing exhibited gate-leakageinduced I-V degradation qualitatively similar to the degradation illustrated in Fig. 2 for Device #1.

Discussion and Summary

The primary mechanism limiting the duration of stable 500 °C electrical operation of the 6H-SiC MESFET was the increased current leakage from the transistor’s Schottky gate-to-channel junction. The increased gate leakage observed with 500 °C anneal time is generally consistent with previously observed behavior wherein this same metal-semiconductor interface gradually changed from Schottky to ohmic behavior with thermal annealing time [2]. Such gate leakage degradation should be greatly reduced via the fabrication of Junction Field Effect Transistors (JFET’s) that use SiC pn junctions as gates instead of metal-semiconductor junction gates. Therefore, fabrication of similar 6H-SiC JFET’s has been initiated with the goal of achieving even longer 500 °C operation. In summary, SiC MESFET electronics and packaging have demonstrated stable continuous electrical operation in a 500 °C oxidizing air ambient for over 2400 hours. Such electronic durability is sufficient for application to hot-section sensor signal conditioning electronics beneficial to turbine engine ground-testing.

Acknowledgements

This work was funded and carried out by NASA Glenn Research Center under the Glennan Microsystems Initiative, Ultra Efficient Engine Technology, Propulsion 21, and NASA Electronic Parts and Packaging programs. The authors greatly appreciate the contributions of E. Benavage, D. Lukco, A. Trunek, D. Androjna, C. Chang, M. Mrdenovich, B. Osborn, G. Hunter, and L. Matus.

Fuente:

http://www.grc.nasa.gov/WWW/SiC/publications/ECSCRM06FET.pdf